For many years RIGOL Technology has been proud to support the test and measurement needs of engineering schools around the world. This is something we are committed to continue as we grow. However, with the industrial market accounting for more than 80% of customers in the industry, to achieve rapid breakthrough and growth, we needed to move beyond the saturated traditional education market.

This was neither a quick or a simple change. It involved a large investment in time and resources to ongoing product testing and innovation. Essentially, we needed to broaden our product line.

As a company that focuses on solving customer problems, we approached this with a solutions mindset. Once we understood the specific problems our customers were facing, we used software and hardware integrated into RIGOL’s existing products to find new ways to apply them.

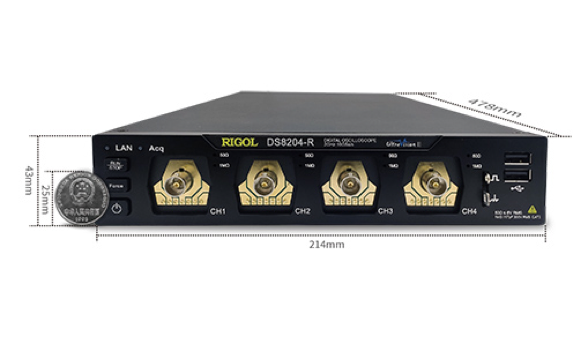

We’ve been working on this process for more than 10 years now, and we’re proud to have recently launched a new digital oscilloscope designed specifically for the industrial market; the DS8000-R series.

To develop this series, our team worked hard to understand the needs of the industrial market and design a solution with many uses in the industrial field. The result is a medium and high-end digital oscilloscope designed to meet customers' complex requirements for synchronous acquisition and testing. Through our own chip technology, we have completed the replacement of domestic products. What’s more, it’s the thinnest 1U high-rack oscilloscope in the world.

There’s been many successful cases of RIGOL improving processes in the industrial field. For example, it has been used in customers’ quantum computation experimental verification tests and high energy physics particle tests. Similarly, the DS8000-R can play a huge role in multi-channel particle detection and multi-channel sensor synchronous acquisition.

Just like every product, throughout the process for developing and testing the DS8000-R series, we looked at it from the user’s perspective. We listened carefully to what challenges our customers face, and what they needed to overcome these. Then, we provided them with safer, more accurate, reliable and easy-to-use electronic test and measurement products and solutions.

For more information on the DS8000-R series.